이진수의 덧셈

간단한 논리연산을 가지고 계산기를 만들수있다.

게이트들을 연결하여 새로운 게이트를 만들 수 있다.

sum 비트

0 + 0 = 0 ,carry는 0

0 + 1 = 1, carry는 0

1 + 0 = 1, carry는 0

1 + 1 = 0, 하지만 carry는 1

- '합'은 두 비트를 더했을 때의 결과이다.

- 이진 덧셈에서는 0과 0을 더하면 0, 1과 0을 더하거나 0과 1을 더하면 1이 된다.

- 1과 1을 더하면 0이 된다 (이 경우, 캐리가 발생한다).

- 예를 들어, 반가산기에서 두 입력 비트가 각각 1과 0일 경우, 합은 1이 됩니다.

- 합은 XOR 게이트를 사용하여 구할 수 있습니다. XOR 게이트는 두 입력이 서로 다를 때 1을 출력하고, 같을 때 0을 출력합니다.

- XOR Gate를 쓰면 계산이 가능하다.

carry 비트

- 기존 논리 게이트로는 sum을 만들 수 없다.

- carry는 두 비트를 더했을 때 발생하는 상위 자리 수로의 이동을 나타낸다.

- 이진 덧셈에서는 1과 1을 더했을 때 캐리가 발생한다. 이는 10진수에서 9와 1을 더했을 때 10이 되는 것과 유사하다. 여기서 '1'이 상위 자리로 올라가는 것처럼, 이진 덧셈에서도 마찬가지로 상위 비트로 1이 캐리된다.

- 캐리는 AND 게이트를 사용하여 구할 수 있다. AND 게이트는 두 입력이 모두 1일 때만 1을 출력한다.

- carry bit는 AND Gate를 쓰면 계산이 가능하다.

가산기

반가산기와 전가산기는 디지털 논리 회로에서 사용되는 기본적인 덧셈 장치이다.

이들은 이진수 덧셈을 수행하는 데 필수적인 구성요소이다.

반가산기 (halfadder)

- 두 bit를 덧셈하는 가산기를 의미

- 반가산기는 두 개의 단일 이진수(비트)를 더하는 가장 간단한 형태의 덧셈 회로이다.

- 이는 두 입력 비트에 대해 두 출력을 생성한다. 하나는 합(Sum)을 위한 것이고, 다른 하나는 캐리(Carry)를 위한 것이다.

- 합(Sum) 출력은 입력 비트의 XOR 게이트에 의해 생성되며, 캐리(Carry) 출력은 입력 비트의 AND 게이트에 의해 생성된다.

- 반가산기는 더 큰 이진수의 덧셈에 대해 캐리 입력을 고려하지 않기 때문에, 여러 비트의 덧셈에 직접 사용하기에는 적합하지 않다.

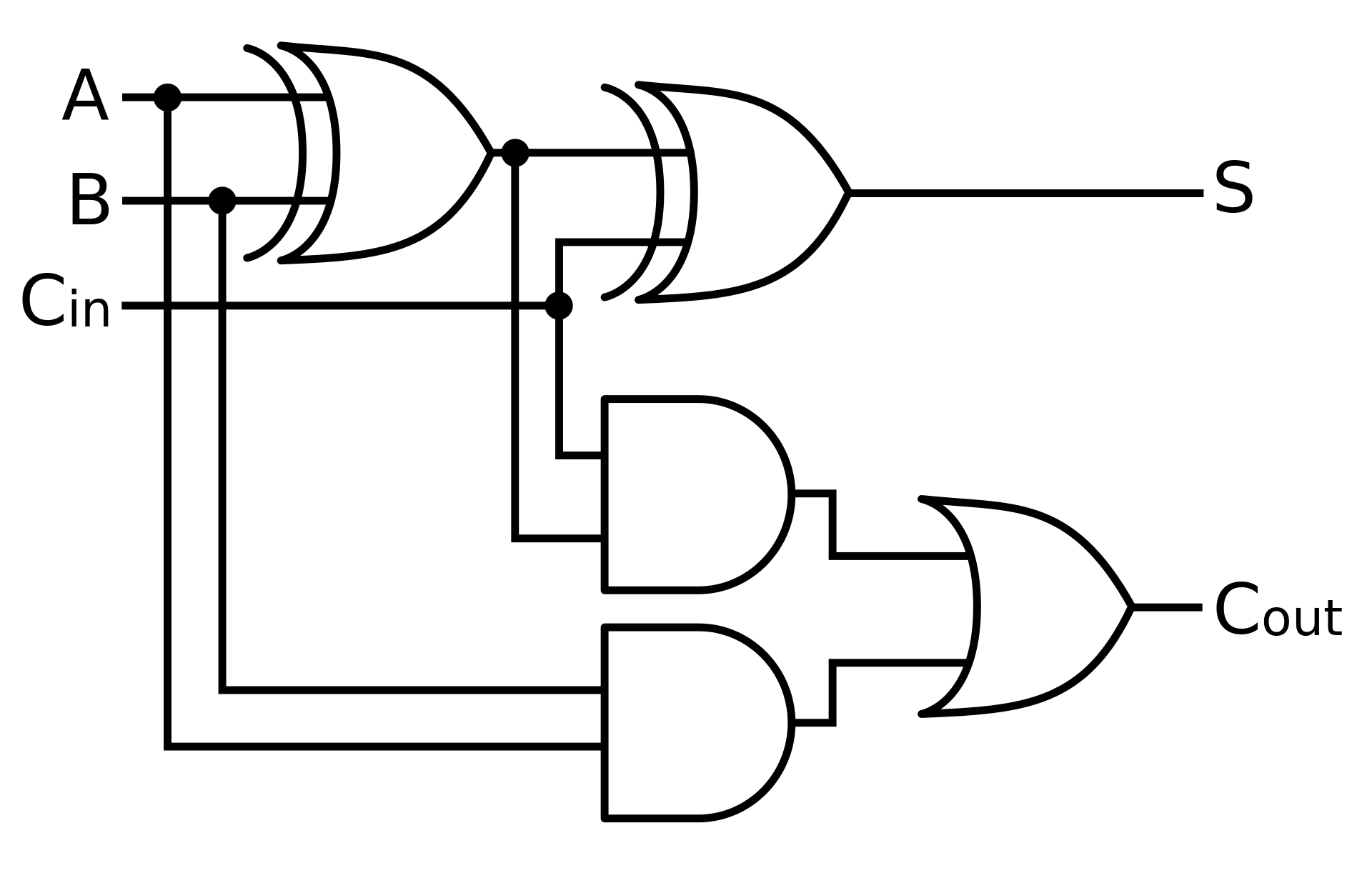

전가산기 (Full Adder)

- 두 bit 외, carry까지 계산할 수 있는 가산기를 의미

- 전가산기는 반가산기의 기능을 확장하여, 세 개의 입력 비트(두 개의 더해지는 비트와 하나의 이전 캐리)에 대해 덧셈을 수행한다.

- 전가산기 역시 두 개의 출력을 제공한다: 합(Sum)과 캐리(Carry).

- 합(Sum)은 세 입력 비트의 XOR 연산에 의해 결정되고, 캐리(Carry)는 입력 비트들 중 어느 것이든 두 개 이상이 1일 경우 생성된다.

- 전가산기는 이진수 덧셈에서 중요한 역할을 하며, 이를 여러 개 연결함으로써 다수의 이진수 비트를 더하는 복잡한 연산을 수행할 수 있다.

'CS > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 컴퓨터 구조, 논리 연산 (1) | 2023.11.24 |

|---|